원하는 FPGA핀으로 시그널을 정의해서 뽑아 보려면, ucf 파일을 건드려야 한다. 물론 친절하게 GUI로 띄워서 클릭으로 선택할 수도 있지만, 기본적인 것은 알아야~~ 기본적인 단어 내용은 아래 글을 참고하자. https://velog.io/@kyoung99u/Xilinx [Xilinx] UCF (User Constraints File) User Constraints File (UCF) 사용자 constraints를 기술하기 위한 AXCII text 파일이다. 모듈 포트 신호들이 어떻게 물리적인 핀에 연결되어야 하는지 기술한다. 즉, 선언한 I/O 포트를 Push button과 User LED로 연 velog.io 예제로 보는 것이 가장 쉽다. 추상적인 내용은 보기도 이해도 어렵다. # ==== Clo..

Xilinx ISE를 통해 memory를 만들어 쓰다 보면, 초기화파일을 지정할 수 있도록 되어 있다.(그냥 소스레벨에서 배열로 선언하고, $readmemh 로 불러들여도, FPGA에 구울때 보면 초기값이 간단하게 들어오긴 하던데 ^^ 무튼) 그 파일 확장자가 .coe 파일이다. 생소하다. 구글링을 통해 찾자. http://sourceforge.net/projects/bin2coe/files/This is the Bin2Coe project ("bin2coe")This project was registered on SourceForge.net on Apr 17, 2011, and is described by the project team as follows:Small utility in C to conv..

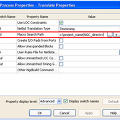

쉽다. 특정 IP나 module에 대한 합성된 ngc 파일을 가지고 있다면, ISE project에 간단하게 넣어서 사용할 수 있다. 더 간단할 수 있는데 툴이 약간 신경을 덜 써주는 것 같기도 하다. (그냥 ngc 파일만 add project 하면 되련만 ㅎ) 인터넷을 검색하면 아래의 글이 나온다. 여기가 정답인듯How-do-I-use-a-NGC-file-toanother-ISE-project그래도 간단히 정리해 보면, 그 다음 프로젝트 폴더에 해당 ngc파일을 복사해 둔다. (다른 폴더에 해도 된다. 그럼 아래 그림에서 해당 Path를 지정해 주면 된다.) 1. 일단 ngc 모듈의 이름을 동일하게 가진 빈파일을 하나 만들어야 한다. 여기서는 Black box로 표현하고 있다. 예제를 간단히 만들면 m..

.ngc 파일에서 vhdl, verilog top 파일 만들기 ISE를 쓰는 경우, ngc파일을 가지고 있어 사용하는 경우 top파일이 필요하기도 하다.간단하게 ngc에서 top 파일 만드는 방법http://www.fpgadeveloper.com/2011/08/how-to-read-an-ngc-netlist-file.html To convert the netlist into VHDL type “netgen -ofmt vhdl filename.ngc“. Netgen will create a filename.vhd file.To convert the netlist into Verilog type “netgen -ofmt verilog filename.ngc“. Netgen will create a filen..