![[verilog] `timescale 1ns/10ps 의미](http://i1.daumcdn.net/thumb/C120x120/?fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcPVgrj%2FbtrkYgofrnB%2FAAAAAAAAAAAAAAAAAAAAAFwG9l26JPD90JUaEyteI-rtSKRhPjWzSOkxtNTKLlX9%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1780239599%26allow_ip%3D%26allow_referer%3D%26signature%3DMC19rXpoUXodDYm3%252F8THRzyhbK4%253D)

Verilog 코딩 중에 첫 번째 줄에 가장 많이 나오는 듯한 timescale 의 의미를 한 번 더 정리해 보자. `timescale 1ns/10ps 앞에 숫자는 작성중인 해당 파일 내에서 쓰이는 숫자들의 단위를 나타냄..즉 #2 이렇게 쓰여있다면 2ns를 나타냄 뒤의 숫자는 시뮬레이터에서 많이 쓰일 것 같은데 코딩에서는 별 효과가..무튼 소수점을 허용하려면 어디까지 해야할까 나타내야 하는데 그 때 쓰이는 최소 단위. 더욱 자세한 설명은 아래글 참고. 원본글이 업데이트가 된지 오래 되어서 여기에 로컬 복사해 둡니다. 저자분께 죄송합니다. [verilog] timescale에 대하여작성자 j0hnch01 [출처] [verilog] timescale에 대하여|작성자 j0hnch01 assign #5 foo..

Verilog 에서 배열 선언은 아래와 같이 하면 된다. 다중 배열의 예를 보자. reg [7:0] a[3]; 이렇게 한다. 앞쪽의 "[7:0]"는 배열을 표현보다는 버스의 비트를 나타내고, 배열을 뒤쪽의 "[3]" 으로 보고 이해하는 것이 쉽다. 즉 위의 예는 8비트짜리 배열 3개을 가지고 있다는 의미 또한 중요한 것은 포트로 뽑아낼 수가 없다는 엄청 불편한 진실.. 즉 module의 input/output으로 쓰기 곤란하다는.. 구체적인 예는 위 참고 사이트 참조 참고 : http://blog.naver.com/beahey/90192889480 [문법] 배열(array) [혼동 문법] 배열(array) 1. Array 와 Register (1) reg [4:0] port (2) reg [4:0] po..

생각보단 쉽다. 자신이 만든 라이브러리 라면 더 쉽겠지만,다른 사람이 만든 라이브러리의 버그를 과감히 수정해 보는 경험을 해보자. (물론 라이브러리 관리자에게 허가를 받아야 하지만)일단, 간단하게 해본 경험을 적어보았다.아래 http://medium.com 을 통해 적은 글을 클릭해서 보자. 그대로 긁어 오려니, CSS가 너무 안맞네. 수정하기는 귀찮고 링크로 대신한다. from : https://medium.com/@bjnhur/be-a-contributor-of-mbed-library-82a1b75fc754Ethernet Library for W5500 ( WIZnet ) 예제로 모두에게 오픈되어 있는 #mbed에 흔적을 남겨보자. 누군가에게 도움이 되지 않아도..되길 바라지만 Be a Contrib..

ARM 에서 밀고 있는 무료 온라인 컴파일 환경사이트 주소는 http://mbed.org 이다.요즘 플랫폼도 많고, 사용자도 많아진 듯. NXP, ST, Freescale 어떤 칩을 쓰던 쉽게 컴파일하고 테스트할 수 있는 환경이다.난 간단한 "Hello World" 수준의 프로그램밖엔 못해봤지만.많이 자동화 되어 있고, 라이브러리도 많이 있다. 한글자료로 찾아보니 거의 하나밖에는 없네..그래도 복사해서 소개 출처 : http://wiki.vctec.co.kr/devboard/mbed 하위 페이지 나열[ARM mbed 강좌] 01. mbed 소개[ARM mbed 강좌] 02. mbed 구입, 유저등록, 기본테스트[ARM mbed 강좌] 03. mbed 소스작성, 컴파일, 업로드[ARM mbed 강좌] 04..

그냥 발표자료이다. 쭉 처음부터 읽어보면 된다.Keil uvision으로 간단히 프로그램 만들고, 디버깅하는 것들, 유용한 기능들에 대한 설명이 쭉 되어 있다. 출처 : Keil Overview - MIT 비슷한 자료지만, 기왕 찾은 것 하나더 첨부"Development Tools for ARM-Powered Devices" - MDK-ARM, 디버그 종류에 따른 기능도 간단히 비교해주고 EVB 그림도 하나 나오고 ^^, 단 2009년 자료라는 것.. 출처 : http://www.emcu.it/KEIL/mdk_4.00_full.pdf ㅋㅋ 짤은 십여년전에 배운 컴파일러책~~~ Compilers by mrjoro

프로그램을 작성하다 보면, 하나의 프로젝트지만 (즉, 거의 비슷한 소스를 사용하는데,) 특정부분때문에 여러 프로젝트로 나누어야 하는 경우가 생긴다. 예를 들면, 공통 라이브러리를 사용하는데 MCU가 달라서 다른 Startup code를 써야 한다면제일 쉽게는 각각 별도의 프로젝트로 만들고 코딩을 하면 된다. 그래도 일목요연하게 하나의 그룹처럼 보이게 하려면..Keil을 쓰는 경우라면, UV4, UV5등을 사용하는 경우라면 "Targets" 이라는 용어를 사용하고 있더라~ Keil의 help 사이트에서 예를 가져와 보자. 출처 : http://www.keil.com/uvision/ide_prj_targets.asp 그림으로 가져왔다.위의 그림의 왼쪽과 오른쪽 처럼 Target MCU가 다른 경우로 나누어서..

ARM SoC 개발 중 버스나 Decoder에 보면 default slave 가 있다. 머냐..메모리 맵상에 할당되지 않은 주소(빈공간)를 접근하는 경우 활성화 되는 모듈이다.이름 그대로 디폴트..역할은 단순하다. HREADYOUT은 물론 잘 띄워줘야 하고, 읽기든 쓰기든 끝이 나게 하려면 꼭 띄워줘야하고또 하나, HRESP에 에러를 띄워주는 것. 왜냐면 여기는 빈공간이니까~~ http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.faqs/ka3445.htmlGeneral: What is a default slave?Applies to: AHBAnswerIf the memory map of a system does not define the full ..

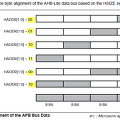

AMBA bus를 사용하는 경우, 바이트별 접근을 위해 판단하는 시그널 생성 코드 (참고용, 책임 못짐 ^^) // Generate byte access from AHB busassign byte0_access = (HSIZE[1] | ((HADDR[1]==1'b0) & HSIZE[0]) | (HADDR[1:0]==2'b00));assign byte1_access = (HSIZE[1] | ((HADDR[1]==1'b0) & HSIZE[0]) | (HADDR[1:0]==2'b01));assign byte2_access = (HSIZE[1] | ((HADDR[1]==1'b1) & HSIZE[0]) | (HADDR[1:0]==2'b10));assign byte3_access = (HSIZE[1] | ((HAD..

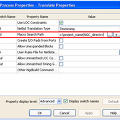

쉽다. 특정 IP나 module에 대한 합성된 ngc 파일을 가지고 있다면, ISE project에 간단하게 넣어서 사용할 수 있다. 더 간단할 수 있는데 툴이 약간 신경을 덜 써주는 것 같기도 하다. (그냥 ngc 파일만 add project 하면 되련만 ㅎ) 인터넷을 검색하면 아래의 글이 나온다. 여기가 정답인듯How-do-I-use-a-NGC-file-toanother-ISE-project그래도 간단히 정리해 보면, 그 다음 프로젝트 폴더에 해당 ngc파일을 복사해 둔다. (다른 폴더에 해도 된다. 그럼 아래 그림에서 해당 Path를 지정해 주면 된다.) 1. 일단 ngc 모듈의 이름을 동일하게 가진 빈파일을 하나 만들어야 한다. 여기서는 Black box로 표현하고 있다. 예제를 간단히 만들면 m..

reference : http://www.ics.uci.edu/~jmoorkan/vhdlref/literals.html 상수 constant FREEZE : integer := 32; constant TEMP : real := 32.0; constant FLAG :bit_vector(0 to 7) := "11111111"; constant MSG : string := "Hello"; 숫자 표현 BIT_8_BUS

제품 링크 : http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,400,897&Prod=NEXYS3FPGA가 조금 작아서, 이정도 레벨에는 간단하게 ARM Slave Peri 정도 테스트가 가능하겠다.보통 Xilinx에서 slice 로 gate count를 표현을 해놓으니 감이 없어서 간단하게 tm으로 적어둔다. UART, PWM, I2C, SPI 머 이런 인터페이스 블럭은 올려서 해 볼 만한 보드다운로드 툴이 따로 제공되니 다른 고민은 좀 덜하고 설계에 집중가능해당 홈페이지에서 필요한 자료 몇개 링크 정보 가져와서 저장5/31/11 Nexys 3 schematicsDownload1/21/14 Nexys 3 reference manualDownload3..

오래된 이야기지만,저장해 두자. 내용은 간단하고 읽기 쉽다. 차이점을 몰라도 코딩에는 문제 없지만. 이런 것이 있다는 정도 =) from : http://web.mit.edu/6.111/www/f2012/The IEEE Verilog 1364-2001 Standard. What's News, and Why You Need It(로컬카피)

Microsemi Application note 에 있는 그림을 잘라 가져온다. 약간 헷갈릴 수 있는데, 그림으로 잘 그려두었다.기본이 4바이트(워드라고 부른다)로 동작을 하니 바이트 동작을 하는 경우 alignment가 신경 쓰인다. 그냥 콱 4바이트 전용으로 동작하면 좋으련만 녹록치 않다 세상은. ^^그림을 보면 이해가 쏙, HADDR의 하위 2비트를 옵셋으로 사용하고, HSIZE가 동작 단위이다.당연히 HSIZE="00" 인 경우 바이트 동작이므로 4가지의 경우가 생기고HSIZE="01" 인 경우 2바이트 단위이므로 2가지의 경우가 생긴다. (상상일 수 있지만, HADDR[1:0] = "00" 이나 "01" 이라도 같은 동작일 듯 하다. 상위비트로 구분할 듯)그리고, HSIZE = "10" 인 경우..