![[verilog] `timescale 1ns/10ps 의미](http://i1.daumcdn.net/thumb/C120x120/?fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcPVgrj%2FbtrkYgofrnB%2FAAAAAAAAAAAAAAAAAAAAAFwG9l26JPD90JUaEyteI-rtSKRhPjWzSOkxtNTKLlX9%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D%252BwsNmcZ95AMSeaseWMqBTlOtCdc%253D)

Verilog 코딩 중에 첫 번째 줄에 가장 많이 나오는 듯한 timescale 의 의미를 한 번 더 정리해 보자. `timescale 1ns/10ps 앞에 숫자는 작성중인 해당 파일 내에서 쓰이는 숫자들의 단위를 나타냄..즉 #2 이렇게 쓰여있다면 2ns를 나타냄 뒤의 숫자는 시뮬레이터에서 많이 쓰일 것 같은데 코딩에서는 별 효과가..무튼 소수점을 허용하려면 어디까지 해야할까 나타내야 하는데 그 때 쓰이는 최소 단위. 더욱 자세한 설명은 아래글 참고. 원본글이 업데이트가 된지 오래 되어서 여기에 로컬 복사해 둡니다. 저자분께 죄송합니다. [verilog] timescale에 대하여작성자 j0hnch01 [출처] [verilog] timescale에 대하여|작성자 j0hnch01 assign #5 foo..

Verilog 에서 배열 선언은 아래와 같이 하면 된다. 다중 배열의 예를 보자. reg [7:0] a[3]; 이렇게 한다. 앞쪽의 "[7:0]"는 배열을 표현보다는 버스의 비트를 나타내고, 배열을 뒤쪽의 "[3]" 으로 보고 이해하는 것이 쉽다. 즉 위의 예는 8비트짜리 배열 3개을 가지고 있다는 의미 또한 중요한 것은 포트로 뽑아낼 수가 없다는 엄청 불편한 진실.. 즉 module의 input/output으로 쓰기 곤란하다는.. 구체적인 예는 위 참고 사이트 참조 참고 : http://blog.naver.com/beahey/90192889480 [문법] 배열(array) [혼동 문법] 배열(array) 1. Array 와 Register (1) reg [4:0] port (2) reg [4:0] po..

오래된 이야기지만,저장해 두자. 내용은 간단하고 읽기 쉽다. 차이점을 몰라도 코딩에는 문제 없지만. 이런 것이 있다는 정도 =) from : http://web.mit.edu/6.111/www/f2012/The IEEE Verilog 1364-2001 Standard. What's News, and Why You Need It(로컬카피)

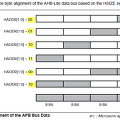

Microsemi Application note 에 있는 그림을 잘라 가져온다. 약간 헷갈릴 수 있는데, 그림으로 잘 그려두었다.기본이 4바이트(워드라고 부른다)로 동작을 하니 바이트 동작을 하는 경우 alignment가 신경 쓰인다. 그냥 콱 4바이트 전용으로 동작하면 좋으련만 녹록치 않다 세상은. ^^그림을 보면 이해가 쏙, HADDR의 하위 2비트를 옵셋으로 사용하고, HSIZE가 동작 단위이다.당연히 HSIZE="00" 인 경우 바이트 동작이므로 4가지의 경우가 생기고HSIZE="01" 인 경우 2바이트 단위이므로 2가지의 경우가 생긴다. (상상일 수 있지만, HADDR[1:0] = "00" 이나 "01" 이라도 같은 동작일 듯 하다. 상위비트로 구분할 듯)그리고, HSIZE = "10" 인 경우..